# QSM

## QUEUED SERIAL MODULE Reference Manual

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. MOTOROLA and the Motorola logo are registered trademarks of Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

© MOTOROLA, INC., 1991, 1996

## TABLE OF CONTENTS

#### Paragraph

Title

Page

#### SECTION 1 FUNCTIONAL OVERVIEW

| 1.1 | Block Diagram | 1- | 1 |

|-----|---------------|----|---|

| 1.2 | Memory Map    | 1- | 2 |

#### **SECTION 2 SIGNAL DESCRIPTIONS**

| 2.1   | SCI Pins                           | 2-1 |

|-------|------------------------------------|-----|

| 2.1.1 | RXD — Receive Data                 | 2-1 |

| 2.1.2 | TXD — Transmit Data                | 2-1 |

| 2.2   | QSPI Pins                          | 2-2 |

| 2.2.1 | PCS[3:0] — Peripheral Chip-Selects | 2-2 |

| 2.2.2 | SS — Slave Select                  |     |

| 2.2.3 | SCK — QSPI Serial Clock            | 2-2 |

| 2.2.4 | MISO — Master In Slave Out         | 2-2 |

| 2.2.5 | MOSI — Master Out Slave In         | 2-2 |

|       |                                    |     |

#### **SECTION 3 CONFIGURATION AND CONTROL**

| 3.1   | Overall QSM Configuration Summary    |      |

|-------|--------------------------------------|------|

| 3.2   | QSM Global Registers                 |      |

| 3.2.1 | QSM Configuration Register (QSMCR)   |      |

| 3.2.2 | QSM Test Register (QTEST)            |      |

| 3.2.3 | QSM Interrupt Level Register (QILR)  |      |

| 3.2.4 | QSM Interrupt Vector Register (QIVR) |      |

| 3.3   | QSM Pin Control Registers            |      |

| 3.3.1 | QSM Port Data Register (PORTQS)      |      |

| 3.3.2 | QSM Pin Assignment Register (PQSPAR) | 3-10 |

| 3.3.3 | QSM Data Direction Register (DDRQS)  | 3-10 |

|       |                                      |      |

#### SECTION 4 QSPI SUBMODULE

| 4.1   | Features                              | 4-1 |

|-------|---------------------------------------|-----|

| 4.1.1 | Programmable Queue                    | 4-1 |

| 4.1.2 | Programmable Peripheral Chip-Selects  | 4-2 |

| 4.1.3 | Wraparound Transfer Mode              | 4-2 |

| 4.1.4 | Programmable Transfer Length          | 4-2 |

| 4.1.5 | Programmable Transfer Delay           | 4-2 |

| 4.1.6 | Programmable Queue Pointer            | 4-2 |

| 4.1.7 | Continuous Transfer Mode              | 4-2 |

| 4.2   | Block Diagram                         | 4-3 |

| 4.3   | QSPI Programmer's Model and Registers | 4-3 |

|       |                                       |     |

#### TABLE OF CONTENTS (Continued) Title

| 4.3.1   | QSPI Control Register 0 (SPCR0) | 4-4  |

|---------|---------------------------------|------|

| 4.3.2   | QSPI Control Register 1 (SPCR1) |      |

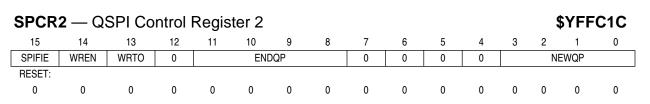

| 4.3.3   | QSPI Control Register 2 (SPCR2) |      |

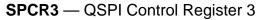

| 4.3.4   | QSPI Control Register 3 (SPCR3) |      |

| 4.3.5   | QSPI Status Register (SPSR)     |      |

| 4.3.6   | QSPI RAM                        |      |

| 4.3.6.1 | Receive Data RAM                |      |

| 4.3.6.2 | Transmit Data RAM               | 4-14 |

| 4.3.6.3 | Command RAM                     | 4-14 |

| 4.4     | Operating Modes and Flowcharts  |      |

| 4.4.1   | Master Mode                     |      |

| 4.4.1.1 | Master Mode Operation           |      |

| 4.4.1.2 | Master Wraparound Mode          |      |

| 4.4.2   | Slave Mode                      |      |

| 4.4.2.1 | Description of Slave Operation  |      |

| 4.4.2.2 | Slave Wraparound Mode           |      |

#### SECTION 5 SCI SUBMODULE

| 5.1     | Features                             | 5-1  |

|---------|--------------------------------------|------|

| 5.2     | SCI Programmer's Model and Registers | 5-2  |

| 5.2.1   | SCI Control Register 0 (SCCR0)       | 5-5  |

| 5.2.2   | SCI Control Register 1 (SCCR1)       | 5-6  |

| 5.2.3   | SCI Status Register (SCSR)           | 5-9  |

| 5.2.4   | SCI Data Register (SCDR)             | 5-12 |

| 5.3     | Transmitter Operation                | 5-13 |

| 5.4     | Receiver Operation                   | 5-15 |

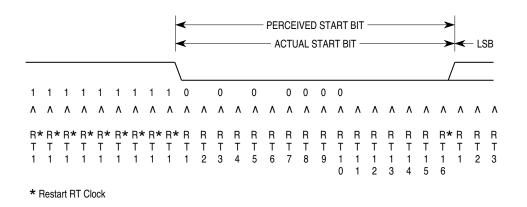

| 5.4.1   | Receiver Bit Processor               | 5-16 |

| 5.4.2   | Receiver Functional Operation        | 5-20 |

| 5.4.2.1 | Idle-Line Detect                     | 5-21 |

| 5.4.2.2 | Receiver Wakeup                      | 5-22 |

|         |                                      |      |

#### APPENDIX A AN1062: USING THE QSPI FOR ANALOG DATA AQUISITION

| A.1 | Introduction                                                   | A-1  |

|-----|----------------------------------------------------------------|------|

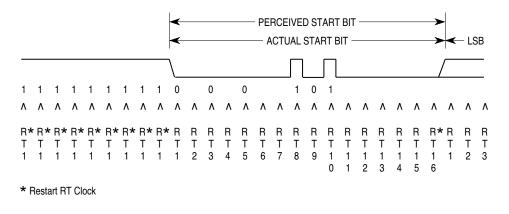

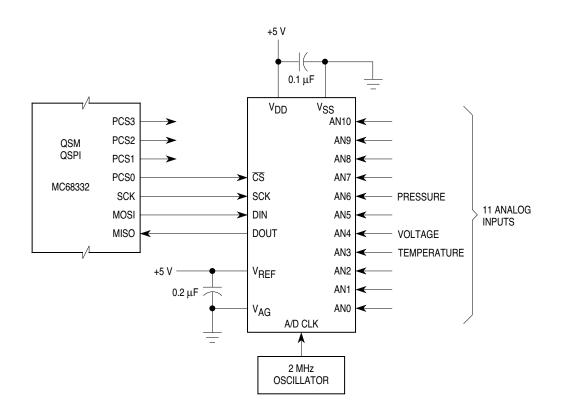

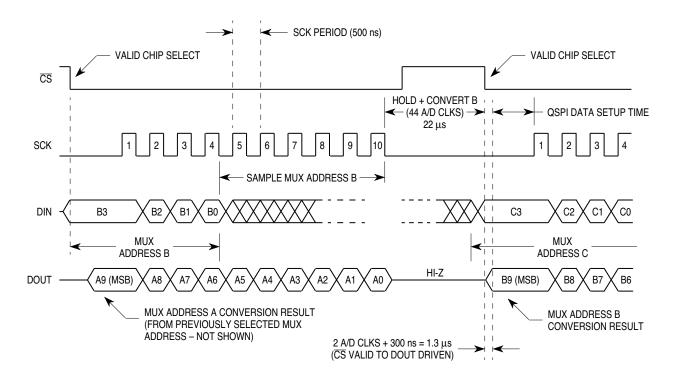

| A.2 | Operation of the MC145040 and MC145050 Family A/D Converters . | A-1  |

| A.3 | Fundamentals of QSPI Operation                                 | A-2  |

| A.4 | Basic System Implementation                                    | A-7  |

| A.5 | Timing Considerations                                          |      |

| A.6 | QSPI Initialization and Operation                              | A-10 |

| A.7 | Other Useful Concepts                                          | A-11 |

| A.8 | References                                                     | A-12 |

Page

#### TABLE OF CONTENTS (Continued) Title

#### Paragraph

Page

#### APPENDIX B QSM MEMORY MAP AND REGISTERS

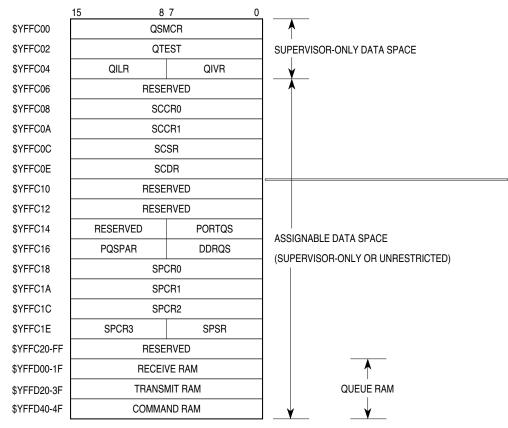

| B.1 | QSM Memory Map | B-1 |

|-----|----------------|-----|

| B.2 | QSM Registers  | B-1 |

#### INDEX

#### TABLE OF CONTENTS (Continued) Title

Paragraph

Page

## LIST OF ILLUSTRATIONS

| Figure | Title                                                             | Page |

|--------|-------------------------------------------------------------------|------|

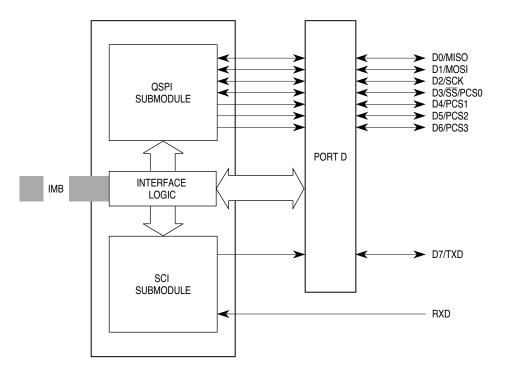

| 1-1    | QSM Block Diagram                                                 | 1-2  |

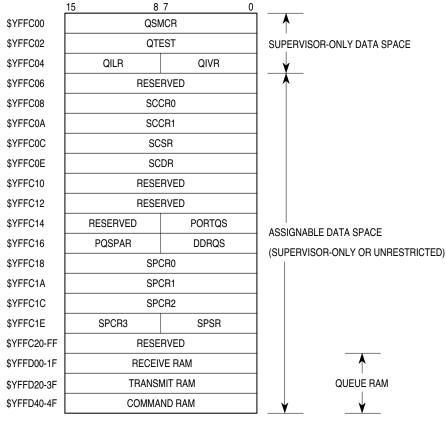

| 1-2    | QSM Memory Map                                                    | 1-3  |

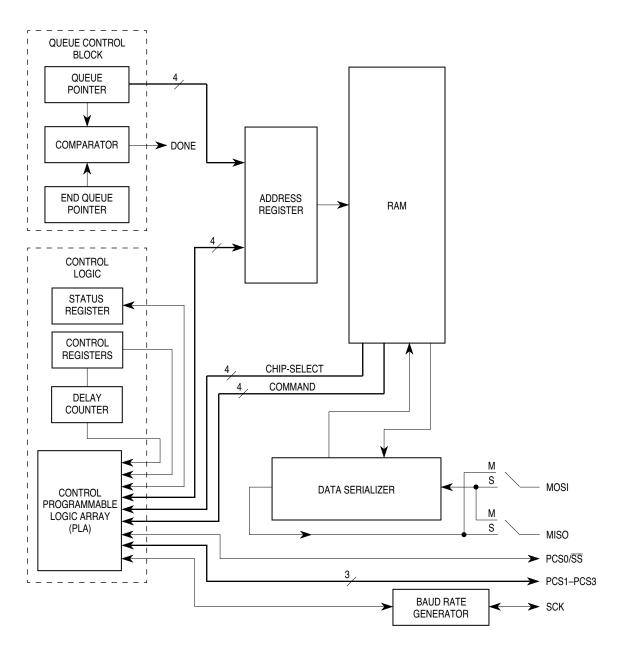

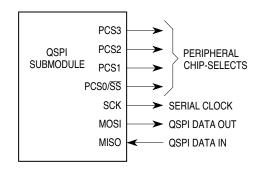

| 4-1    | QSPI Submodule Diagram                                            | 4-3  |

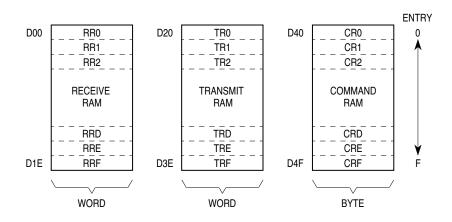

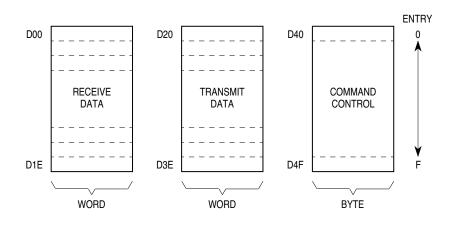

| 4-2    | Organization of the QSPI RAM                                      | 4-13 |

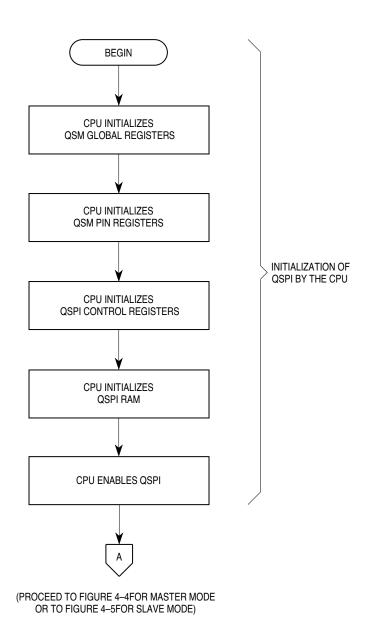

| 4-3    | Flowchart of QSPI Initialization Operation                        | 4-18 |

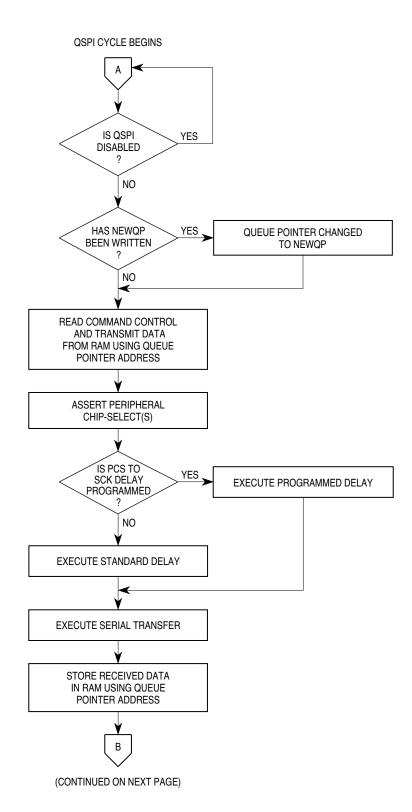

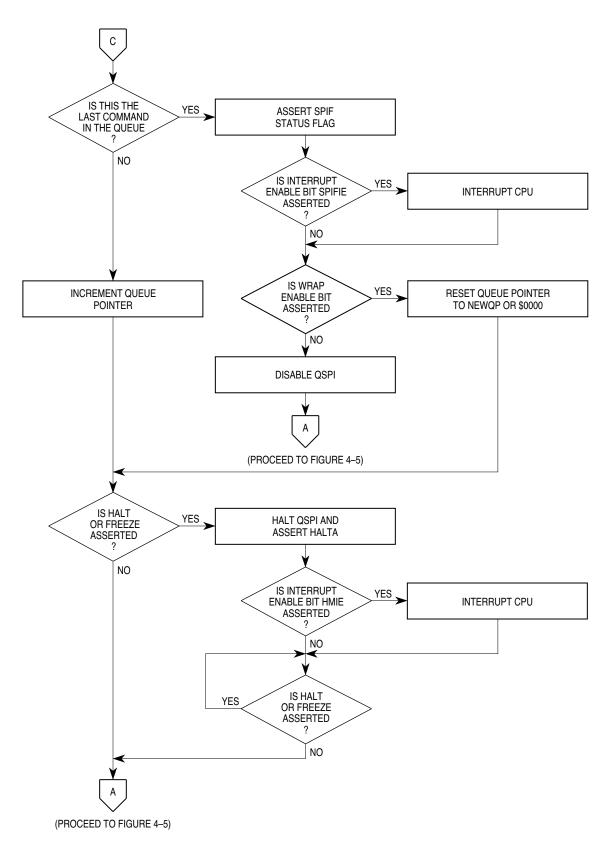

| 4-4    | Flowchart of QSPI Master Operation (Part 1)                       | 4-19 |

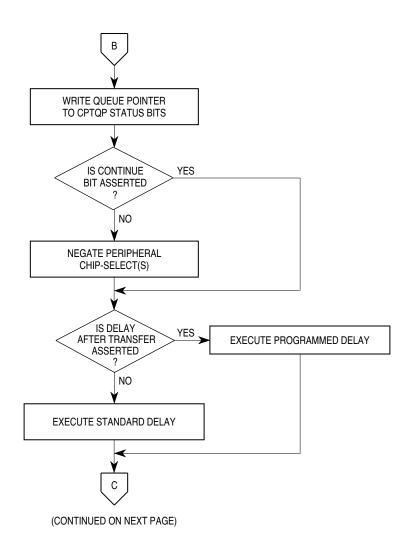

| 4-4    | Flowchart of QSPI Master Operation (Part 2)                       | 4-20 |

| 4-4    | Flowchart of QSPI Master Operation (Part 3)                       | 4-21 |

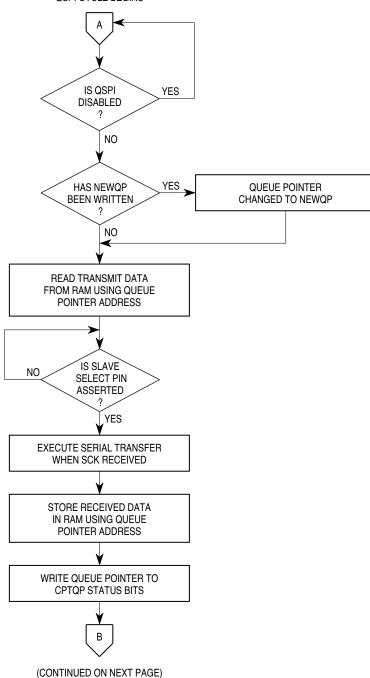

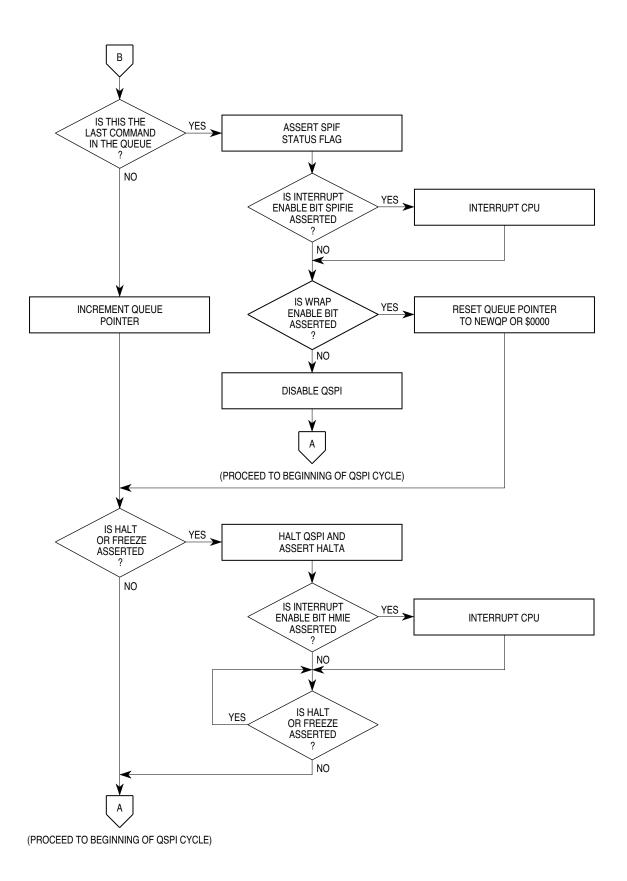

| 4-5    | Flowchart of QSPI Slave Operation (Part 1)                        |      |

| 4-5    | Flowchart of QSPI Slave Operation (Part 2)                        | 4-23 |

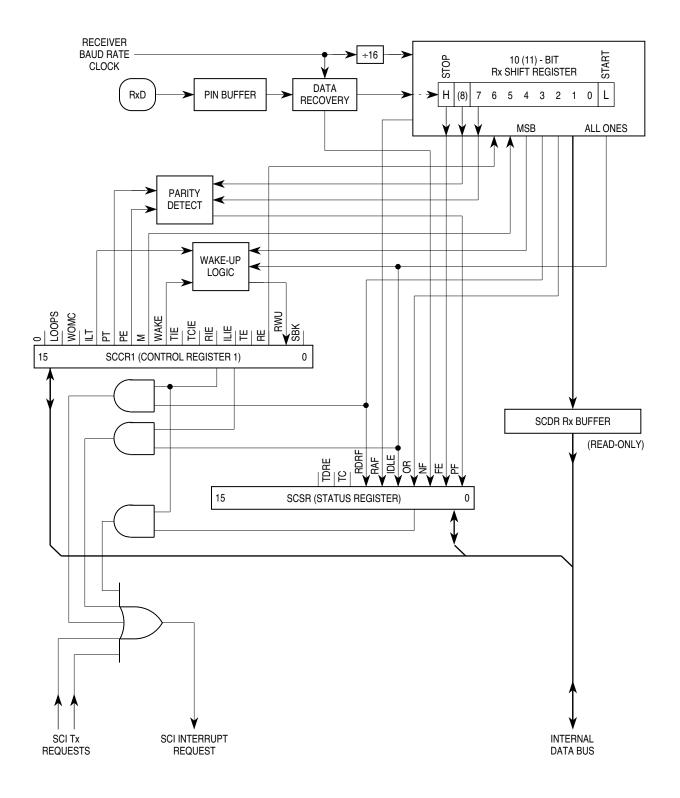

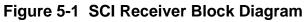

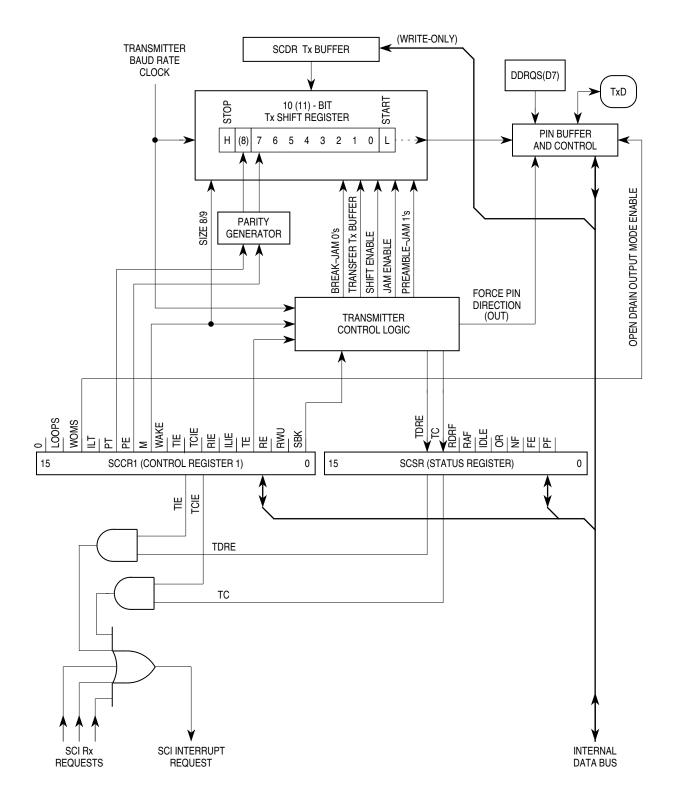

| 5-1    | SCI Receiver Block Diagram                                        | 5-3  |

| 5-2    | SCI Transmitter Block Diagram                                     | 5-4  |

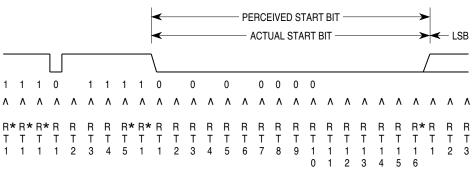

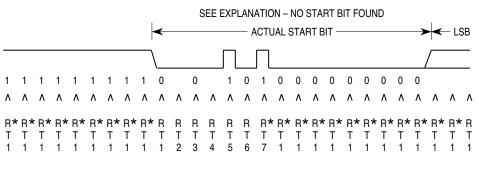

| 5-3    | Start Search Example 1                                            | 5-17 |

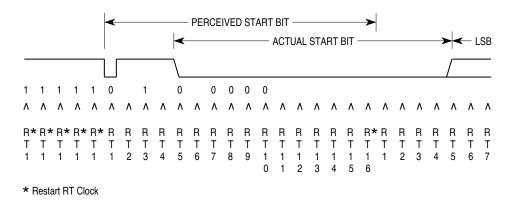

| 5-4    | Start Search Example 2                                            | 5-17 |

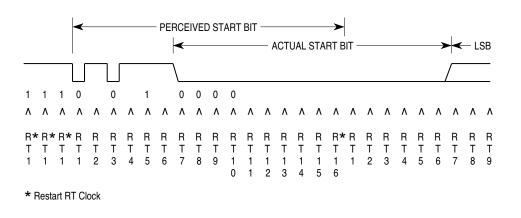

| 5-5    | Start Search Example 3                                            | 5-18 |

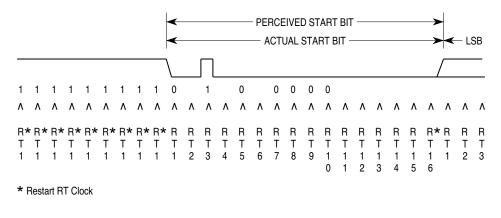

| 5-6    | Start Search Example 4                                            | 5-18 |

| 5-7    | Start Search Example 5                                            | 5-19 |

| 5-8    | Start Search Example 6                                            | 5-19 |

| 5-9    | Start Search Example 7                                            | 5-20 |

| A-1    | MC145050 Pinout                                                   |      |

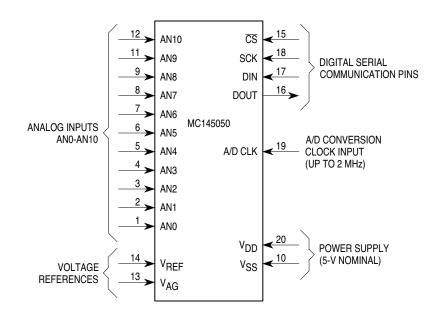

| A-2    | Master Mode Representation of the QSPI                            | A-3  |

| A-3    | Organization of the QSPI Ram                                      | A-3  |

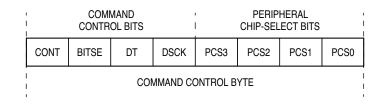

| A-4    | Command Control Byte                                              | A-4  |

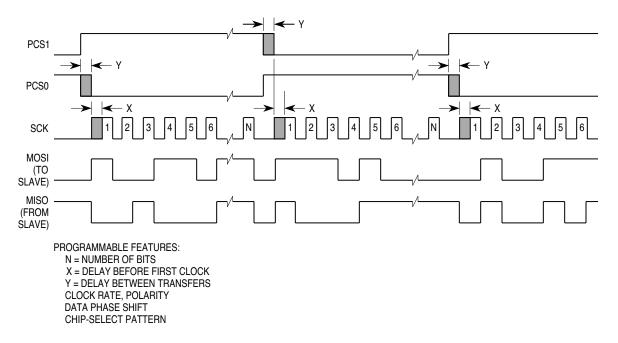

| A-5    | Basic QSPI Master Mode Timing Diagram                             | A-4  |

| A-6    | QSPI Programmer's Model                                           |      |

| A-7    | Basic Serial A/D Data Acquisition System                          | A-7  |

| A-8    | MC14050 Conversion and Transfer Timing                            | A-8  |

| A-9    | Use of QSPI to Control A/D Conversions - 2 MHz A/D (Sheet 1 of 4) | A-13 |

| A-9    | Use of QSPI to Control A/D Conversions - 2 MHz A/D (Sheet 2 of 4) | A-14 |

| A-9    | Use of QSPI to Control A/D Conversions 2 MHz A/D (Sheet 3 of 4)   | A-15 |

| A-9    | Use of QSPI to Control A/D Conversions 2 MHz A/D (Sheet 4 of 4)   | A-16 |

| A-10   | Example Queue Structure and Operation Flow                        | A-17 |

| A-11   | Example Subqueue Structure and Operation Flow                     | A-18 |

#### LIST OF ILLUSTRATIONS (Continued) Title

Figure

Page

## LIST OF TABLES

| Tab | le Title                                         | Page  |

|-----|--------------------------------------------------|-------|

|     | External Pin Inputs/Outputs to the SC            |       |

| 2-2 | External Pin Inputs/Outputs to the QSPI          |       |

| 3-1 | QSM Register Summary                             |       |

| 3-2 | Bit/Field Quick Reference Guide                  |       |

| 3-3 | QSM Global Registers                             |       |

|     | QSM Pin Control Registers                        |       |

| 4-1 | QSPI Registers                                   |       |

| 4-2 | Bits per Transfer if Command Control Bit BITSE = | 1 4-5 |

| 4-3 | Examples of SCK Frequencies                      |       |

| 5-1 | SCI Register                                     |       |

| 5-2 | Examples of SCI Baud Rates                       |       |

|     | M and PE Bit Fields                              |       |

#### LIST OF TABLES (Continued) Title

Table

## SECTION 1 FUNCTIONAL OVERVIEW

The queued serial module (QSM) provides the microcontroller unit (MCU) with two serial communication interfaces divided into two submodules: the queued serial peripheral interface (QSPI) and the serial communications interface (SCI).

The QSPI is a full-duplex, synchronous serial interface for communicating with peripherals and other MCUs. It is enhanced by the addition of a queue for receive and transmit data.

The SCI is a full-duplex universal asynchronous receiver transmitter (UART) serial interface. These submodules operate independently.

This section provides a block diagram, memory map, pin description, and register descriptions of the QSM, with a breakdown of both the QSPI and SCI submodules. Operation of the QSPI submodule includes master mode and slave mode. For a detailed description refer to **4.4.1 Master Mode** and **4.4.2 Slave Mode**.

In addition, operation of the SCI submodule is divided into transmit and receive. A description of these operations is given in **5.3 Transmitter Operation** and **5.4 Receiver Operation**. To aid in grasping an understanding of the numerous bits and fields of the registers that appear throughout the text, a quick reference guide identifies all bit/field acronyms. (Refer to **Table 3-2**.)

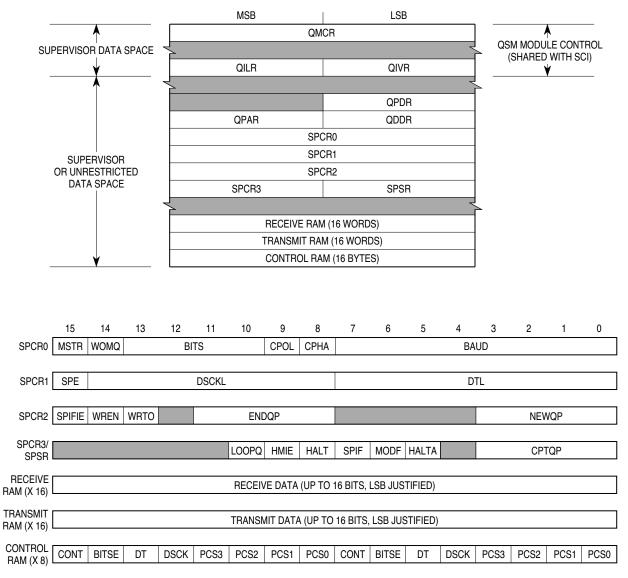

#### 1.1 Block Diagram

**Figure 1-1** depicts the major components of the QSM, which consist of the global registers, logic control, and the QSPI and SCI submodules. Refer to **SECTION 4 QSPI SUBMODULE** and **SECTION 5 SCI SUBMODULE** for further definition of these components.

Figure 1-1 QSM Block Diagram

#### 1.2 Memory Map

The QSM memory map is comprised of the global registers, the QSPI and SCI control and status registers, and the QSPI RAM as shown in **Figure 1-2**. For an accurate location of the QSM memory in the MCU memory map, refer to appropriate CPU manual. The QSM memory map may be divided into two segments: supervisor-only data space and assignable data space.

Y = m111 where m is the modmap bit in the SIM MCR (Y = 7 or F).

Figure 1-2 QSM Memory Map

The supervisor-only data space segment contains the QSM global registers. These registers define parameters needed by the QSM to integrate with the MCU. Access to these registers is permitted only when the CPU is operating in supervisor mode (CPU status register, S-bit = 1).

Assignable data space can be either restricted to supervisor-only access or unrestricted to both supervisor and user accesses. The supervisor (SUPV) bit in the QSM module configuration register (QSMCR) designates the assignable data space as either supervisor or unrestricted. If SUPV is set, then the space is designated as supervisoronly space. Access is then permitted only when the CPU is operating in supervisor mode. All attempts to read supervisor data spaces when not in supervisor mode (CPU status register, S-bit = 0) return a value of zero, and all attempts to write have no effect. If SUPV is clear, both user and supervisor accesses are permitted. To clear SUPV in the QSMCR, the CPU must be in supervisor mode (CPU status register, S-bit = 1). Refer to Processing States in the appropriate CPU manual for more information on supervisor mode.

The QSM assignable data space segment contains the submodules, QSPI and SCI, control/status registers, and the QSPI RAM. All registers and RAM may be accessed

on byte, word, and long-word boundaries. The 80 bytes of static RAM are distinct from the QSM register set. All bytes not used by the QSPI may be used as general-purpose RAM. When operating, the QSPI submodule uses three non-contiguous blocks of the 80-byte RAM for receive, transmit, and control data. More information on the QSPI RAM can be found in **4.3.6 QSPI RAM**.

The contents of most locations in the memory map may be rewritten with the identical value to that location, with one exception. (Refer to **4.3.3 QSPI Control Register 2 (SPCR2)**.) Writing a different value to certain control registers when a submodule using that register is enabled can cause unpredictable results. For predictable operation, if register bits are to be changed, the CPU should disable the submodule in an orderly fashion before altering the registers.

## **SECTION 2 SIGNAL DESCRIPTIONS**

The QSM has nine external pins, as shown in **Figure 1-1**. Eight of the pins, if not in use for their submodule function, can be used as general-purpose I/O port pins. The ninth pin, RXD, is an input-only pin used exclusively by the SCI submodule.

The QSM pin control registers — DDRQS, QSM pin assignment register (PQSPAR, and QSM port data register (PORTQS) — affect pins being used as general-purpose I/O pins. The QSPI control register 0 (SPCR0) has one bit that affects seven pins employed as general-purpose output pins. Within this register the wired-OR mode (WOMQ) control bit determines whether MISO, MOSI, SCK, and PCS[3:0] function as open-drain output pins or as normal output pins, regardless of their use as general-purpose I/O pins or as QSPI output pins. Likewise, the SCI control register 1 (SCCR1) has one bit that affects the TXD pin when it is employed as a general-purpose output. In this register the wired-OR mode (WOMS) control bit determines whether TXD functions as an open-drain output pin or a normal output pin, regardless of this pin's use as a general-purpose output pin or as an SCI output pin. Refer to **3.3 QSM Pin Control Registers** for more information on these registers.

#### 2.1 SCI Pins

There are two pins associated with the SCI, the RXD and TXD pins. The SCI pins and their functions are listed in **Table 2-1**.

#### 2.1.1 RXD — Receive Data

This dedicated input signal furnishes serial data input to the SCI. The RXD pin cannot be used for general-purpose I/O.

#### 2.1.2 TXD — Transmit Data

This signal is the serial data output from the SCI. TXD is available as a general-purpose I/O pin when the SCI transmitter is disabled. When used as general-purpose I/ O, TXD may be configured either as input or output as determined by the TXD bit in the QSM register DDRQS. The state of the TXD bit is ignored while the SCI is enabled. The TXD pin is enabled for SCI use by the transmitter enable bit (TE) in the SCI Control Register 1 (SCCR1). Refer to **5.2.2 SCI Control Register 1 (SCCR1)** for more information.

| Pin Names     | Mnemonics | Mode                 | Function                    |

|---------------|-----------|----------------------|-----------------------------|

| Receive Data  | RXD       | Receiver Disabled    | Not Used                    |

|               |           | Receiver Enabled     | Serial Data Input to SCI    |

| Transmit Data | TXD       | Transmitter Disabled | General-Purpose I/O         |

|               |           | Transmitter Enabled  | Serial Data Output from SCI |

#### Table 2-1 External Pin Inputs/Outputs to the SC

#### 2.2 QSPI Pins

Seven pins are associated with the QSPI. When not needed for a QSPI application, they may be configured as general-purpose I/O pins. **Table 2-2** identifies the QSPI pins and their functions. QSM register DDRQS determines whether the pins are designated as input or output. The user must initialize DDRQS for the QSPI to function correctly.

#### 2.2.1 PCS[3:0] — Peripheral Chip-Selects

These bidirectional signals provide QSPI peripheral chip-selects.

#### 2.2.2 SS — Slave Select

Assertion of this bidirectional signal selects the QSPI when in slave mode. This is the same pin as PCS0.

#### 2.2.3 SCK — QSPI Serial Clock

This bidirectional signal furnishes the clock from the QSPI in Master mode or furnishes the clock to the QSPI in slave mode.

#### 2.2.4 MISO — Master In Slave Out

This bidirectional signal furnishes serial data input to the QSPI in master mode, and serial data output from the QSPI in slave mode.

#### 2.2.5 MOSI — Master Out Slave In

This bidirectional signal furnishes serial data output from the QSPI in master mode, and serial data input to the QSPI in slave mode.

| Pin Names                                                        | Mnemonics        | Mode            | Function                                                  |

|------------------------------------------------------------------|------------------|-----------------|-----------------------------------------------------------|

| Master In Slave Out                                              | MISO             | Master<br>Slave | Serial Data Input to QSPI<br>Serial Data Output from QSPI |

| Master Out Slave In                                              | MOSI             | Master<br>Slave | Serial Data Output from QSPI<br>Serial Data Input to QSPI |

| Serial Clock                                                     | SCK <sup>1</sup> | Master<br>Slave | Clock Output from QSPI Clock<br>Input to QSPI             |

| Peripheral Chip-Selects                                          | PCS[3:1]         | Master          | Outputs Select Peripheral(s)                              |

| Peripheral Chip-Select <sup>2</sup><br>Slave Select <sup>3</sup> | PCS0/<br>SS      | Master<br>Slave | Output Selects Peripheral(s)<br>Input Selects the QSPI    |

| Slave Select <sup>4</sup>                                        | SS               | Master          | May Cause Mode Fault                                      |

#### Table 2-2 External Pin Inputs/Outputs to the QSPI

NOTES:

1. All QSPI pins (except SCK) can be used as general-purpose I/O if they are not used by the QSPI while the QSPI is operating.

2. An output (PCS0) when the QSPI is in master mode.

3. An input  $(\overline{SS})$  when the QSPI is in slave mode.

4. An input  $(\overline{SS})$  when the QSPI is in master mode; useful in multimaster systems.

## **SECTION 3 CONFIGURATION AND CONTROL**

Registers of the QSM are divided into four categories: QSM global registers, QSM pin control registers, QSPI submodule registers, and SCI submodule registers. The QSPI and SCI registers are defined in **4.3 QSPI Programmer's Model and Registers** and **5.2 SCI Programmer's Model and Registers**, respectively. Writes to unimplemented bits have no meaning or effect, and reads from unimplemented bits always return a logic zero value.

The modmap bit of the system integration module (SIM) module configuration register (MCR) defines the most significant bit (ADDR23) of the address, shown in each register figure as Y (Y = 7 or F). This bit, concatenated with the rest of the address given, forms the absolute address of each register.

**Table 3-1** is a summary of the registers, bits, and reset states for the full QSM module.

As previously mentioned, **Table 3-2** is a quick reference guide to all the bits/fields of the QSM module. Along with the function, the register and register location of each bit/ field are identified.

#### Table 3-1 QSM Register Summary

|                              | 15                           | 14    | 13   | 12     | 11    | 10    | 9       | 8         | 7              | 6               | 5               | 4               | 3                | 2              | 1               | 0               |

|------------------------------|------------------------------|-------|------|--------|-------|-------|---------|-----------|----------------|-----------------|-----------------|-----------------|------------------|----------------|-----------------|-----------------|

| QSMCR<br>\$YFFC00            | STOP                         | FRZ1  | FRZ0 | 0      | 0     | 0     | 0       | 0         | SUPV           | 0               | 0               | 0               |                  | IA             | RB              |                 |

| RESET:                       | 0                            | 0     | 0    | 0      | 0     | 0     | 0       | 0         | 1              | 0               | 0               | 0               | 0                | 0              | 0               | 0               |

| QTEST<br>\$YFFC02            | 0                            | 0     | 0    | 0      | 0     | 0     | 0       | 0         | 0              | 0               | 0               | 0               | TSBD             | SYNC           | TQSM            | TMM             |

| RESET:                       | 0                            | 0     | 0    | 0      | 0     | 0     | 0       | 0         | 0              | 0               | 0               | 0               | 0                | 0              | 0               | 0               |

| QILR/QIVR<br>\$YFFC04        | 0                            | 0     |      | ILQSPI |       |       | ILSCI   |           |                | •               |                 | IN              | TV               |                | •               |                 |

| RESET:                       | 0                            | 0     | 0    | 0      | 0     | 0     | 0       | 0         | 0              | 0               | 0               | 0               | 1                | 1              | 1               | 1               |

| \$YFFC06                     |                              |       |      |        |       |       |         | RESE      | RVED           |                 |                 |                 | •                |                |                 |                 |

| SCCR0<br>\$YFFC08            | 0                            | 0     | 0    |        |       |       |         |           |                | SCBR            |                 |                 |                  |                |                 |                 |

| RESET:                       | 0                            | 0     | 0    | 0      | 0     | 0     | 0       | 0         | 0              | 0               | 0               | 0               | 0                | 1              | 0               | 0               |

| SCCR1<br>\$YFFC0A            | 0                            | LOOPS | WOMS | ILT    | PT    | PE    | М       | WAKE      | TIE            | TCIE            | RIE             | ILIE            | TE               | RE             | RWU             | SBK             |

| RESET:                       | 0                            | 0     | 0    | 0      | 0     | 0     | 0       | 0         | 0              | 0               | 0               | 0               | 0                | 0              | 0               | 0               |

| SCSR<br>\$YFFC0C             | 0                            | 0     | 0    | 0      | 0     | 0     | 0       | TDRE      | TC             | RDRF            | RAF             | IDLE            | OR               | NF             | FE              | PF              |

| RESET:                       | 0                            | 0     | 0    | 0      | 0     | 0     | 0       | 1         | 1              | 0               | 0               | 0               | 0                | 0              | 0               | 0               |

| SCDR<br>\$YFFC0E             | 0                            | 0     | 0    | 0      | 0     | 0     | 0       | R8/T8     | R7/T7          | R6/T6           | R5/T5           | R4/T4           | R3/T3            | R2/T2          | R1/T1           | R0/T0           |

| RESET:                       | 0                            | 0     | 0    | 0      | 0     | 0     | 0       | U         | U              | U               | U               | U               | U                | U              | U               | U               |

| \$YFFC10                     |                              |       |      |        |       |       |         | RESE      | RVED           |                 |                 |                 |                  |                |                 |                 |

| \$YFFC12                     |                              |       |      |        |       |       |         | RESE      | RVED           |                 |                 |                 |                  |                |                 |                 |

| PORTQS<br>\$YFFC14           | 0                            | 0     | 0    | 0      | 0     | 0     | 0       | 0         | DATA7<br>(TXD) | DATA6<br>(PCS3) | DATA5<br>(PCS2) | DATA4<br>(PCS1) | DATA3<br>(PCS0*) | DATA2<br>(SCK) | DATA1<br>(MOSI) | DATA0<br>(MISO) |

| RESET:                       | 0                            | 0     | 0    | 0      | 0     | 0     | 0       | 0         | 0              | 0               | 0               | 0               | 0                | 0              | 0               | 0               |

| PQSPAR/<br>DDRQS<br>\$YFFC16 | 0                            | PCS3  | PCS2 | PCS1   | PCS0* | 0     | MOSI    | MISO      | TXD            | PCS3            | PCS2            | PCS1            | PCS0*            | SCK            | MOSI            | MISO            |

| RESET:                       | 0                            | 0     | 0    | 0      | 0     | 0     | 0       | 0         | 0              | 0               | 0               | 0               | 0                | 0              | 0               | 0               |

| SPCR0<br>\$YFFC18            | MSTR                         | WOMQ  |      | Bľ     | TS    |       | CPOL    | CPHA      |                |                 | 1               | SP              | BR               | <u>I</u>       |                 | 1               |

| RESET:                       | 0                            | 0     | 0    | 0      | 0     | 0     | 0       | 1         | 0              | 0               | 0               | 0               | 0                | 1              | 0               | 0               |

| SPCR1<br>\$YFFC1A            | SPE                          |       |      |        | DSCKL | 1     |         |           |                |                 |                 | D               | TL               |                |                 |                 |

| RESET:                       | 0                            | 0     | 0    | 0      | 0     | 1     | 0       | 0         | 0              | 0               | 0               | 0               | 0                | 1              | 0               | 0               |

| SPCR2<br>\$YFFC1C            | SPIFIE                       | WREN  | WRTO | 0      |       | END   | DQP     |           | 0              | 0               | 0               | 0               |                  | NEV            | WQP             |                 |

| RESET:                       | 0                            | 0     | 0    | 0      | 0     | 0     | 0       | 0         | 0              | 0               | 0               | 0               | 0                | 0              | 0               | 0               |

| SPCR3/<br>SPSR               | 0                            | 0     | 0    | 0      | 0     | LOOPQ | HMIE    | HALT      | SPIF           | MODF            | HALTA           | 0               |                  | CP             | TQP             |                 |

| \$YFFC1E<br>RESET:           | 0                            | 0     | 0    | 0      | 0     | 0     |         |           | 0              | 0               | 0               | 0               | 0                | 0              | 0               | 0               |

| \$YFFC20-                    | 0                            | 0     | 0    | U      | 0     | 0     | 0       | 0<br>RESE | 0<br>RVED      | 0               | 0               | 0               | 0                | 0              | 0               | 0               |

| \$YFFCFF<br>RECEIVE          | QSPI RECEIVE DATA (16 WORDS) |       |      |        |       |       |         |           |                |                 |                 |                 |                  |                |                 |                 |

| RAM<br>\$YFFD00-<br>\$YFFD1F |                              |       |      |        |       |       |         |           |                |                 |                 |                 |                  |                |                 |                 |

| TRANSMIT                     |                              |       |      |        |       |       | QSPI TR | ANSMIT [  | DATA (16       | WORDS)          |                 |                 |                  |                |                 |                 |

| \$YFFD20-<br>\$YFFD3F        |                              |       |      |        |       |       |         |           |                |                 |                 |                 |                  |                |                 |                 |

| COMMAND                      | CONT                         | BITSE | DT   | DSCK   | PCS3  | PCS2  | PCS1    | PCS0*     | CONT           | BITSE           | DT              | DSCK            | PCS3             | PCS2           | PCS1            | PCS0*           |

| \$YFFD40–<br>\$YFFD4F        |                              |       |      |        |       |       |         |           |                |                 |                 |                 |                  |                |                 |                 |

Y = m111, where m is the modmap bit in the module configuration register for the SIM (Y = \$7 or \$F).

\* The PCS0 bit listed above represents the dual-function  $PCS0/\overline{SS}$ .

| Bit/Field Mnemonic | Function                                                                        | Register                | Register Location |  |  |

|--------------------|---------------------------------------------------------------------------------|-------------------------|-------------------|--|--|

| SPBR               | Serial Clock Baud Rate                                                          | SPCR0                   | QSPI              |  |  |

| BITS               | Bits Per Transfer                                                               | SPCR0                   | QSPI              |  |  |

| BITSE              | Bits Per Transfer Enable                                                        | QSPI RAM                | QSPI              |  |  |

| SCBR               | Baud Rate                                                                       | SCCR0                   | SCI               |  |  |

| CONT               | Continue                                                                        | QSPI RAM                | QSPI              |  |  |

| СРНА               | Clock Phase                                                                     | SPCR0                   | QSPI              |  |  |

| CPOL               | Clock Polarity                                                                  | SPCR0                   | QSPI              |  |  |

| CPTQP              | Completed Queue Pointer                                                         | SPSR                    | QSPI              |  |  |

| DSCK               | Peripheral Select Chip (PSC) to Serial<br>Clock (SCK) Delay                     | QSPI RAM                | QSPI              |  |  |

| DSCKL              | Delay before Serial Clock (SCK)                                                 | SPCR1                   | QSPI              |  |  |

| DT                 | Delay after Transfer                                                            | QSPI RAM                | QSPI              |  |  |

| DTL                | Length of Delay after Transfer                                                  | SPCR1                   | QSPI              |  |  |

| ENDQP              | Ending Queue Pointer                                                            | SPCR2                   | QSPI              |  |  |

| FE                 | Framing Error Flag                                                              | SCSR                    | SCI               |  |  |

| FRZ[1:0]           | Freeze1–0                                                                       | QSMCR                   | QSM               |  |  |

| HALT               | Halt                                                                            | SPCR3                   | QSPI              |  |  |

| HALTA              | Halt Acknowledge Flag                                                           | SPSR                    | QSPI              |  |  |

| HMIE               | Halt Acknowledge Flag (HALTA) and<br>Mode Fault Flag (MODF) Interrupt<br>Enable | SPCR3                   | QSPI              |  |  |

| IARB               | Interrupt Arbitration Identification<br>Number                                  | QSMCR                   | QSM               |  |  |

| IDLE               | Idle Line Detected Flag                                                         | SCSR                    | SCI               |  |  |

| ILIE               | Idle Line Interrupt Enable                                                      | SCCR1                   | SCI               |  |  |

| ILQSPI             | Interrupt Level for QSPI                                                        | QILR                    | QSM               |  |  |

| ILSCI              | Interrupt Level of SCI                                                          | QILR                    | QSM               |  |  |

| ILT                | Idle Line Detect Type                                                           | SCCR1                   | SCI               |  |  |

| INTV               | Interrupt Vector                                                                | QIVR                    | QSM               |  |  |

| LOOPS              | SCI Loop Mode                                                                   | SCCR1                   | SCI               |  |  |

| LOOPQ              | QSPI Loop Mode                                                                  | SPCR3                   | QSPI              |  |  |

| М                  | Mode Select (8/9 Bit)                                                           | SCCR1                   | SCI               |  |  |

| MISO               | Master In Slave Out                                                             | PQSPAR/DDRQS/<br>PORTQS | QSM               |  |  |

| MODF               | Mode Fault Flag                                                                 | SPSR                    | QSPI              |  |  |

| MOSI               | Master Out Slave In                                                             | PQSPAR/DDRQS/<br>PORTQS | QSM               |  |  |

| MSTR               | Master/Slave Mode Select                                                        | SPCR0                   | QSPI              |  |  |

| NEWQP              | New Queue Pointer Value                                                         | SPCR2                   | QSPI              |  |  |

| NF                 | Noise Error Flag                                                                | SCSR                    | SCI               |  |  |

| OR                 | Overrun Error Flag                                                              | SCSR                    | SCI               |  |  |

| PCS0/SS            | Peripheral Chip-Select/Slave Select                                             | PQSPAR/DDRQS/<br>PORTQS | QSM               |  |  |

| PCS[3:1]           | Peripheral Chip-Selects                                                         | PQSPAR/DDRQS/<br>PORTQS | QSM               |  |  |

| PE                 | Parity Enable                                                                   | SCCR1                   | SCI               |  |  |

| PF                 | Parity Error Flag                                                               | SCSR                    | SCI               |  |  |

| PT                 | Parity Type                                                                     | SCCR1                   | SCI               |  |  |

| R[8:0]             | Receive 8–0                                                                     | SCDR                    | SCI               |  |  |

Table 3-2 Bit/Field Quick Reference Guide (Sheet 1 of 2)

| <b>Bit/Field Mnemonic</b> | Function                           | Register     | Register Location |  |  |

|---------------------------|------------------------------------|--------------|-------------------|--|--|

| RAF                       | Receiver Active Flag               | SCSR         | SCI               |  |  |

| RDRF                      | Receive Data Register Full Flag    | SCSR         | SCI               |  |  |

| RE                        | Receiver Enable                    | SCCR1        | SCI               |  |  |

| RIE                       | Receiver Interrupt Enable          | SCCR1        | SCI               |  |  |

| RWU                       | Receiver Wakeup                    | SCCR1        | SCI               |  |  |

| SBK                       | Send Break                         | SCCR1        | SCI               |  |  |

| SCK                       | Serial Clock                       | DDRQS/PORTQS | QSM               |  |  |

| SPE                       | QSPI Enable                        | SPCR1        | QSPI              |  |  |

| SPIF                      | QSPI Finished Flag                 | SPSR         | QSPI              |  |  |

| SPIFIE                    | SPI Finished Interrupt Enable      | SPCR2        | QSPI              |  |  |

| STOP                      | Stop                               | QSMCR        | QSM               |  |  |

| SUPV                      | Supervisor/Unrestricted            | QSMCR        | QSM               |  |  |

| SYNC                      | SCI Baud Clock Sync Signal         | QTEST        | QSM               |  |  |

| T[8:0]                    | Transmit 8–0                       | SCDR         | SCI               |  |  |

| TC                        | Transmit Complete Flag             | SCSR         | SCI               |  |  |

| TCIE                      | Transmit Complete Interrupt Enable | SCCR1        | SCI               |  |  |

| TDRE                      | Transmit Data Register Empty Flag  | SCSR         | SCI               |  |  |

| TE                        | Transmit Enable                    | SCCR1        | SCI               |  |  |

| TIE                       | Transmit Interrupt Enable          | SCCR1        | SCI               |  |  |

| TMM                       | Test Memory Map                    | QTEST        | QSM               |  |  |

| TQSM                      | Test QSM Enable                    | QTEST        | QSM               |  |  |

| TSBD                      | SPI Test Scan Path Select          | QTEST        | QSM               |  |  |

| TXD                       | Transmit Data                      | DDRQS/PORTQS | QSM               |  |  |

| WAKE                      | Wakeup Type                        | SCCR1        | SCI               |  |  |

| WOMQ                      | Wired-OR Mode for QSPI Pins        | SPCR0        | QSPI              |  |  |

| WOMS                      | Wired-OR Mode for SCI Pins         | SCCR1        | SCI               |  |  |

| WREN                      | Wrap Enable                        | SPCR2        | QSPI              |  |  |

| WRTO                      | Wrap To Select                     | SPCR2        | QSPI              |  |  |

|                           |                                    |              |                   |  |  |

Table 3-2 Bit/Field Quick Reference Guide (Sheet 2 of 2)

#### 3.1 Overall QSM Configuration Summary

After reset, the QSM remains in an idle state, requiring initialization of several registers before any serial operations may begin execution. The following registers, fields, and bits are fully described later in this section. A general sequence guide for initialization follows:

#### • QSMCR (refer to 3.2.1 QSM Configuration Register (QSMCR)

This register must be initialized to properly configure:

- Interrupt arbitration identification number used by the entire QSM module

- Supervisor/unrestricted bit (SUPV)

- FREEZE and/or STOP configuration; which should remain cleared to zero for normal operation.

- QIVR and QILR (refer to 3.2.3 QSM Interrupt Level Register (QILR) and 3.2.4 QSM Interrupt Vector Register (QIVR)

These registers are written to choose the base vector number for the entire QSM module and individual interrupt levels for the QSPI and SCI submodules. • PORTQS and DDRQS (refer to 3.3.1 QSM Port Data Register (PORTQS) and 3.3.3 QSM Data Direction Register (DDRQS)

The pin control registers should be initialized in the order PORTQS and then DDRQS, thus establishing the default state and direction of the QSM pins.

For configuration of the QSPI submodule, initialize as follows:

- RAM (refer to **4.3.6 QSPI RAM**)

- PQSPAR (refer to 3.3.2 QSM Pin Assignment Register (PQSPAR)

Assignment of appropriate pins to the QSPI must be made with this register.

#### • SPCR0 (refer to 4.3.1 QSPI Control Register 0 (SPCR0)

The system designer must choose a transfer rate (baud) for operation in master mode. an appropriate clock phase, clock polarity, and the number of bits to be transferred in a serial operation. Master/slave mode select (MSTR) must be set to configure the QSPI for master mode or cleared to configure operation in slave mode. WOMQ should be set to enable or cleared to disable wired-OR mode operation.

- SPCR1 (refer to 4.3.2 QSPI Control Register 1 (SPCR1)

- SPE must be set to enable the QSPI; this register should be written last.

- DTL allows the user to program a delay after any serial transfer, which is invoked by the DT bit for any serial transfer.

- DSCKL allows the user to set a delay before SCK (after PCS valid), which is invoked by the DSCK bit for any transfer.

- SPCR2 (refer to 4.3.3 QSPI Control Register 2 (SPCR2)

- NEWQP and ENDQP, respectively, determine the beginning of a gueue and the number of serial transfers (up to 16) to be considered a complete queue.

- WREN is set to enable queue wraparound, and WRTO helps determine the address used in wraparound mode.

- SPIFIE is set to enable interrupts when SPIF is asserted.

- SPCR3 (refer to 4.3.4 QSPI Control Register 3 (SPCR3)

HALT may be used for program debug, and HMIE is set to enable CPU interrupts when HALTA or MODF is asserted; LOOPQ is set only to enable a feedback loop that can be used for self-test mode.

For configuration of the SCI submodule, initialize as follows:

#### • SCCR0 (refer to 5.2.1 SCI Control Register 0 (SCCR0)

The system designer must choose a transfer rate (baud) for serial transfer operation.

- SCCR1 (refer to 5.2.2 SCI Control Register 1 (SCCR1)

- The type of serial frame (8- or 9-bit) and the use of parity must be determined by M, PE, and PT.

- For receive operation, the system designer must consider use and type of wakeup (WAKE, RWU, ILT, ILIE). The receiver must be enabled (RE) and, usually, RIE should be set.

- For transmit operation, the transmitter must be enabled (TE) and, usually, TIE should be set. The use of wired-OR mode (WOMS) must also be decided.

Once the transmitter is configured, data is not sent until TDRE and TC are cleared. To clear TDRE and TC, the SCSR read must be followed by a write to SCDR (either the lower byte or the entire word).

#### 3.2 QSM Global Registers

The QSM global registers contain system parameters used by both the QSPI and the SCI submodules. These registers define parameters used by the QSM to interface with the CPU and other system modules. The four global registers are listed in **Table 3-3**.

| Address  | Name  | Usage                         |

|----------|-------|-------------------------------|

| \$YFFC00 | QSMCR | QSM Configuration Register    |

| \$YFFC02 | QTEST | QSM Test Register             |

| \$YFFC04 | QILR  | QSM Interrupt Level Register  |

| \$YFFC05 | QIVR  | QSM Interrupt Vector Register |

Table 3-3 QSM Global Registers

#### 3.2.1 QSM Configuration Register (QSMCR)

QSMCR contains parameters for interfacing to the CPU and the intermodule bus (IMB). This register can be modified only when the CPU is in supervisor mode.

| <b>QSMCR</b> — QSM Configuration Register |

|-------------------------------------------|

|-------------------------------------------|

#### \$YFFC00

| 15     | 14   | 13   | 12 | 11 | 10 | 9 | 8 | 7    | 6 | 5 | 4 | 3 | 2   | 1  | 0 |

|--------|------|------|----|----|----|---|---|------|---|---|---|---|-----|----|---|

| STOP   | FRZ1 | FRZ0 | 0  | 0  | 0  | 0 | 0 | SUPV | 0 | 0 | 0 |   | IAI | RB |   |

| RESET: |      |      |    |    |    |   |   |      |   |   |   |   |     |    |   |

| 0      | 0    | 0    | 0  | 0  | 0  | 0 | 0 | 1    | 0 | 0 | 0 | 0 | 0   | 0  | 0 |

STOP — Stop Enable

1 = QSM clock operation stopped

0 = Normal QSM clock operation

STOP places the QSM into a low power state by disabling the system clock in most parts of the module. QSMCR is the only register guaranteed to be readable while STOP is asserted. The QSPI RAM is not readable; however, writes to RAM or any register are guaranteed valid while STOP is asserted. STOP may be negated by the CPU and by reset.

The system software must stop each submodule before asserting STOP to avoid complications at restart and to avoid data corruption. The SCI submodule receiver and transmitter should be disabled, and the operation should be verified for completion before asserting STOP. The QSPI submodule should be stopped by asserting the HALT bit in SPCR3 and by asserting STOP after the HALTA flag is set.

#### FRZ1 — Freeze1

- 1 = Halt the QSM (on a transfer boundary)

- 0 = Ignore the FREEZE signal on the IMB

FRZ1 determines what action is taken by the QSM when the FREEZE signal of the IMB is asserted. FREEZE is asserted whenever the CPU enters the background mode.

MOTOROLA

#### WARNING

Ignoring the FREEZE signal can cause unpredictable results in the background mode operation of the QSM, because the CPU is unable to service interrupt requests in this mode. If FRZ1 equals one when the FREEZE line is asserted, the QSM comes to an orderly halt on a transfer boundary as if HALT had been asserted. The output pins continue to drive their last state. Once the FREEZE signal is negated, the QSM module restarts automatically.

FRZ0 — Freeze0

Reserved for future enhancement.

Bits [12:8] - Not Implemented

SUPV — Supervisor/Unrestricted

1 = Supervisor access

All registers in the QSM are placed in supervisor-only space. For any access from within user mode, address acknowledge (AACK) is not returned and the bus cycle is transferred externally.

0 = User access

Because the QSM contains a mix of supervisor and user registers, AACK returns for accesses with either supervisor or user mode, and the bus cycle remains internal. If a supervisor-only register is accessed in user mode, the module responds as if an access had been made to an unimplemented register location.

SUPV defines the assignable QSM registers as either supervisor-only data space or unrestricted data space.

Bits [6:4] — Not Implemented

IARB — Interrupt Arbitration Identification Number

Each module that generates interrupts, including the QSM, must have an IARB field. The value in this field is used to arbitrate for the IMB when two or more modules generate simultaneous interrupts of the same priority level. No two modules can share the same IARB value. The reset value of the IARB field is \$0, which prevents the QSM from arbitrating during an interrupt acknowledge cycle (IACK). The IARB field should be initialized by system software to a value between \$F (highest priority) and \$1 (lowest priority). Otherwise, any interrupts generated are identified by the CPU as spurious.

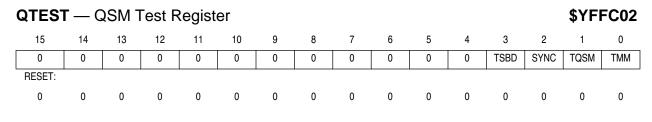

#### 3.2.2 QSM Test Register (QTEST)

QTEST is used in testing the QSM. Accesses to QTEST must be made while the MCU is in test mode. Test mode is for manufacturing use only. Applications should not use this register or enter test mode.

#### TSBD — SPI Test Scan Path Select

- 1 = Enable delay to SCK scan path

- 0 = Enable SPI baud clock scan path

#### SYNC — SCI Baud Clock Synchronization Signal

- 1 = Inhibit SCI source signal (QCSCI1)

- 0 = Activate SCI source signal

#### TQSM — QSM Test Enable

- 1 = Enable QSM to send test scan paths

- 0 = Disable scan path

#### TMM — Test Memory Map

- 1 = QSM responds to test memory addresses

- 0 = QSM responds to QSM memory addresses

#### 3.2.3 QSM Interrupt Level Register (QILR)

The QILR determines the priority level of interrupts requested by the QSM and the vector used when acknowledging an interrupt. Separate fields exist to hold the interrupt levels for the QSPI and the SCI submodules. Priority is used to determine which interrupt is serviced first when two or more modules or external peripherals simultaneously request an interrupt. This register may be accessed only when the CPU is in supervisor mode.

#### **QILR** — QSM Interrupt Level Register

#### \$YFFC04

| 15     | 14                                     | 13 | 12 | 11 | 10 | 9 | 8 | 7 |       | 0 |

|--------|----------------------------------------|----|----|----|----|---|---|---|-------|---|

| 0      | 0 0 ILQSPI ILSCI                       |    |    |    |    |   |   |   | QIVR* |   |

| RESET: |                                        |    |    |    |    |   |   |   |       | , |

| 0      | 0 0 0 0 0 0 0                          |    |    |    |    |   |   |   |       |   |

| * QI   | * QIVR — QSM Interrupt Vector Register |    |    |    |    |   |   |   |       |   |

## ILQSPI — Interrupt Level for QSPI

ILQSPI determines the priority level of all QSPI interrupts. This field should be programmed to a value between \$0 (interrupts disabled) and \$7 (highest priority). If both the QSPI and the SCI modules contain the same priority level (not equal to zero) and both modules simultaneously request interrupt servicing, the QSPI is given priority.

#### ILSCI — Interrupt Level of SCI

ILSCI determines the priority level of all SCI interrupts. This field should be programmed to a value between \$0 (interrupts disabled) and \$7 (highest priority).

#### 3.2.4 QSM Interrupt Vector Register (QIVR)

At reset, QIVR is initialized to \$0F, which corresponds to the uninitialized interrupt vector in the exception table. This vector is selected until QIVR is written. QIVR should be programmed to one of the user-defined vectors (\$40-\$FF) during initialization of the QSM. After initialization, QIVR determines which two vectors in the exception vector table are to be used for QSM interrupts. The QSPI and SCI submodules have separate interrupt vectors adjacent to each other. Both submodules use the same interrupt vector with the least significant bit (LSB) determined by the submodule causing the interrupt. The value of INTV0 used during an IACK cycle is supplied by the bus interface unit (BIU). During an IACK, INTV[7:1] are driven on the DATA[7:1] lines. The INTV0 drives line DATA0 with a zero for an SCI interrupt and with a one for a QSPI interrupt. Writes to INTV0 have no meaning or effect. Reads of INTV0 return a value of one.

| <b>QIVR</b> — QSM Interrupt Vector Register |   |   |   |   |      |        | \$YF | FC05 |   |

|---------------------------------------------|---|---|---|---|------|--------|------|------|---|

| 15                                          | 8 | 7 | 6 | 5 | 4    | 3      | 2    | 1    | 0 |

| QILR*                                       |   |   |   |   | INTV | /[7:0] |      |      |   |

| RESET:                                      |   |   |   |   |      |        |      |      |   |

|                                             |   | 0 | 0 | 0 | 0    | 1      | 1    | 1    | 1 |

INTVO is set to a logic level one when the QSPI generates an interrupt and set to a logic level zero when the SCI generates an interrupt.

\* QILR — QSM Interrupt Level Register

#### 3.3 QSM Pin Control Registers

**Table 3-3** identifies the three pin control registers of the QSM. The QSM determines the use of nine pins, eight of which form a parallel port on the MCU. Although these pins are used by the serial subsystems, any pin may alternately be assigned as general-purpose I/O on a pin by pin basis. For use of these pins as general-purpose I/O, they must not be assigned to the QSPI submodule in register PQSPAR. To avoid briefly driving incorrect data, the first byte to be output should be written before register DDRQS is configured for any output pins. DDRQS should then be written to determine the direction of data flow on the pins and to output the value contained in register PORTQS for all pins defined as outputs. Subsequent data for output is then written to PORTQS.

| Address  | Name   | Usage                       |

|----------|--------|-----------------------------|

| \$YFFC15 | PORTQS | QSM Port Data Register      |

| \$YFFC16 | PQSPAR | QSM Pin Assignment Register |

| \$YFFC17 | DDRQS  | QSM Data Direction Register |

#### 3.3.1 QSM Port Data Register (PORTQS)

PORTQS determines the actual input or output value of a QSM port pin if the pin is defined in PQSPAR as general-purpose I/O. All QSM port pins may be used as general-purpose I/O. Writes to this register affect the pins defined as outputs; reads of this register return the actual value of the pins.

| <b>PORTQS</b> — QSM Port Data Register |   |                |   |                 |                 |                    | \$YFF          | FC15            |                 |

|----------------------------------------|---|----------------|---|-----------------|-----------------|--------------------|----------------|-----------------|-----------------|

| 15                                     | 8 | 7              | 6 | 5               | 4               | 3                  | 2              | 1               | 0               |

| RESERVED                               |   | DATA7<br>(TXD) |   | DATA5<br>(PCS2) | DATA4<br>(PCS1) | DATA3<br>(PCS0/SS) | DATA2<br>(SCK) | DATA1<br>(MOSI) | DATA0<br>(MISO) |

| RESET:                                 |   |                |   |                 |                 |                    |                |                 |                 |

|                                        |   | 0              | 0 | 0               | 0               | 0                  | 0              | 0               | 0               |

#### 3.3.2 QSM Pin Assignment Register (PQSPAR)

PQSPAR determines which of the QSPI pins, with the exception of the SCK pin, are actually used by the QSPI submodule, and which pins are available for general-purpose I/O. Pins may be assigned to the QSPI or to function as general-purpose I/O on a pin-by-pin basis. QSPI pins designated by PQSPAR as general-purpose I/O are controlled only by DDRQS and PORTQS and the QSPI has no effect on these pins. PQS-PAR does not affect the operation of the SCI submodule.

| PQSPAR — QSM Pin | Assignment Register |

|------------------|---------------------|

|                  | Assignment Register |

#### \$YFFC16

|   | 15    | 14   | 13   | 12   | 11      | 10 | 9    | 8    | 7 |        | 0 |

|---|-------|------|------|------|---------|----|------|------|---|--------|---|

|   | 0     | PCS3 | PCS2 | PCS1 | PCSO/SS | 0  | MOSI | MISO |   | DDRQS* |   |

| R | ESET: |      |      |      |         |    |      |      |   |        |   |

|   | 0     | 0    | 0    | 0    | 0       | 0  | 0    | 0    |   |        |   |

#### Bit 15 — Not Implemented

TE in register SCCR1 determines whether the TXD pin is controlled by the SCI or functions as a general-purpose I/O pin.

PCS[3:1] — Peripheral Chip-Selects 3–1

#### PCS0/SS — Peripheral Chip-Select 0/Slave Select

These bits determine whether the associated QSM port pins function as general-purpose I/O pins or are assigned to the QSPI submodule.

#### Bit 10 — Not Implemented

(When the QSPI is enabled, the SCK pin is required.)

- MOSI Master Out Slave In

- MISO Master In Slave Out

These bits determine whether the associated QSM port pin functions as a general-purpose I/O pin or is assigned to the QSPI submodule.

#### 3.3.3 QSM Data Direction Register (DDRQS)

DDRQS sets each I/O pin, except for TXD, as an input or an output regardless of whether the QSPI submodule is enabled or disabled. All QSM pins are configured during reset as general-purpose inputs. (The QSPI and SCI are disabled.) The RXD pin remains an input pin dedicated to the SCI submodule and does not function as a general-purpose I/O pin.

#### DDRQS — QSM Data Direction Register

#### \$YFFC17

| 15     |         | 8 | 7   | 6    | 5    | 4    | 3       | 2   | 1    | 0    |

|--------|---------|---|-----|------|------|------|---------|-----|------|------|

|        | PQSPAR* |   | TXD | PCS3 | PCS2 | PCS1 | PCS0/SS | SCK | MOSI | MISO |

| RESET: |         |   |     |      |      |      |         |     |      | ,    |

|        |         |   | 0   | 0    | 0    | 0    | 0       | 0   | 0    | 0    |

\* PQSPAR — QSM Pin Assignment Register

TXD — Transmit Data

This bit determines the direction of the TXD pin (input or output), only if the SCI transmitter is disabled. If the SCI transmitter is enabled, the TXD bit is ignored, and the TXD pin is forced to function as an output.

PCS[3:1] — Peripheral Chip-Selects 3–1

PCS0/SS — Peripheral Chip-Select 0/Slave Select

- SCK Serial Clock

- MOSI Master Out Slave In

- MISO Master In Slave Out

Refer to 4.4.2 Slave Mode for additional details on this pin.

All of the above bits determine the QSPI port pin operation to be input or output.

1 = Output

0 = Input

## **SECTION 4 QSPI SUBMODULE**

The QSPI submodule communicates with external peripherals and other MCUs via synchronous serial bus. The QSPI is fully compatible with the serial peripheral interface (SPI) systems found on other Motorola devices such as the M68HC11 and M68HC05 Families. It has all of the capabilities of the SPI system as well as several new features. The following paragraphs describe the features, block diagram, pin descriptions, programmer's model (memory map) inclusive of registers, and the master and slave operation of the QSPI.

#### 4.1 Features

Standard SPI features are listed below, followed by a list of the additional features offered on the QSPI:

- Full-Duplex, Three-Wire Synchronous Transfers

- Half-Duplex, Two-Wire Synchronous Transfers

- Master or Slave Operation

- Programmable Master Bit Rates

- Programmable Clock Polarity and Phase

- End-of-Transmission Interrupt Flag

- Master-Master Mode Fault Flag

- Easily Interfaces to Simple Expansion Parts (A/D converters, EEPROMS, display drivers, etc.)

QSPI-Enhanced features are as follows:

- Programmable Queue up to 16 preprogrammed transfers

- Programmable Peripheral Chip-Selects four pins select up to 16 SPI chips

- Wraparound Transfer Mode for autoscanning of serial A/D (or other) peripherals, with no CPU overhead

- Programmable Transfer Length from 8–16 bits inclusive

- Programmable Transfer Delay from 1 µs to 0.5 ms (at 16.78 MHz)

- Programmable Queue Pointer

- Continuous Transfer Mode up to 256 bits

#### 4.1.1 Programmable Queue

A programmable queue allows the QSPI to perform up to 16 serial transfers without CPU intervention. Each transfer corresponds to a queue entry containing all the information needed by the QSPI to independently complete one serial transfer. This unique feature greatly reduces CPU/QSPI interaction, resulting in increased CPU and system throughput.

#### 4.1.2 Programmable Peripheral Chip-Selects

Four peripheral chip-select pins allow the QSPI to access up to 16 independent peripherals by decoding the four peripheral chip-select signals. Up to four independent peripherals can be selected by direct connection to a chip-select pin. The peripheral chip-selects simplify interfacing to two or more serial peripherals by providing dedicated peripheral chip-select signals, alleviating the need for CPU intervention.

#### 4.1.3 Wraparound Transfer Mode

Wraparound transfer mode allows automatic, continuous re-execution of the preprogrammed queue entries. Newly transferred data replaces previously transferred data. Wraparound simplifies interfacing with A/D converters by automatically providing the CPU with the latest A/D conversions in the QSPI RAM. Consequently, serial peripherals appear as memory-mapped parallel devices to the CPU.

#### 4.1.4 Programmable Transfer Length

The number of bits in a serial transfer is programmable from eight to 16 bits, inclusive. For example, ten bits could be used for communicating with an external 10-bit A/D converter. Likewise, a vacuum fluorescent display driver might require a 12-bit serial transfer. The programmable length simplifies interfacing to serial peripherals that require different data lengths.

#### 4.1.5 Programmable Transfer Delay

An inter-transfer delay may be programmed from approximately 1 to 500  $\mu$ s (using a 16.78-MHz system clock). For example, an A/D converter may require time between transfers to complete a new conversion. The default delay is 1  $\mu$ s (17 clocks at 16.78-MHz). The programmable length of delay simplifies interfacing to serial peripherals that require delay time between data transfers.

#### 4.1.6 Programmable Queue Pointer

The QSPI has a pointer that identifies the queue location containing the data for the next serial transfer. The CPU can switch from one task to another in the QSPI by writing to the queue pointer, changing the location in the queue that is to be transferred next. Otherwise, the pointer increments after each serial transfer. By segmenting the queue, multiple-task support can be provided by the QSPI.

#### 4.1.7 Continuous Transfer Mode

The continuous transfer mode allows the user to send and receive an uninterrupted bit stream with a peripheral. A minimum of 8 bits and a maximum of 256 bits may be transferred in a single burst without CPU intervention. Longer transfers are possible; however, minimal CPU intervention is required to prevent loss of data. A 1  $\mu$ s pause (using a 16.78-MHz system clock) is inserted between each queue entry transfer.

#### 4.2 Block Diagram

Figure 4-1 provides a block diagram of the QSPI submodule components.

Figure 4-1 QSPI Submodule Diagram

#### 4.3 QSPI Programmer's Model and Registers

The programmer's model (memory map) for the QSPI submodule consists of the QSM global and pin control registers (refer to **3.2 QSM Global Registers** and **3.3 QSM Pin Control Registers**), four QSPI control registers, one status register, and the 80-byte QSPI RAM. **Table 4-1** lists the registers and the QSPI RAM of the programmer's model. All of the registers and RAM can be read and written by the CPU. The four control

registers must be initialized in proper order before the QSPI is enabled to ensure defined operation. Only the control registers must adhere to the order of sequence prescribed in **3.1 Overall QSM Configuration Summary**. Write register SPCR1 last when setting up the QSPI, as this register contains the QSPI enable bit (SPE). Asserting this bit starts the QSPI. QSPI control registers are reset to a defined state and may then be changed by the CPU. Reset values are shown below each register.

| Address     | Name  | Usage                          |  |  |  |  |  |

|-------------|-------|--------------------------------|--|--|--|--|--|

| \$YFFC18, 9 | SPCR0 | QSPI Control Register 0        |  |  |  |  |  |

| \$YFFC1A, B | SPCR1 | QSPI Control Register 1        |  |  |  |  |  |

| \$YFFC1C, D | SPCR2 | QSPI Control Register 2        |  |  |  |  |  |

| \$YFFC1E    | SPCR3 | QSPI Control Register 3        |  |  |  |  |  |

| \$YFFC1F    | SPSR  | QSPI Status Register           |  |  |  |  |  |

| \$YFFD00-1F | RAM   | QSPI Receive Data (16 Words)   |  |  |  |  |  |

| \$YFFD20-3F | RAM   | QSPI Transmit Data (16 Words)  |  |  |  |  |  |

| \$YFFD40-4F | RAM   | QSPI Command Control (8 Words) |  |  |  |  |  |

#### **Table 4-1 QSPI Registers**

In general, rewriting the same value into a control register does not affect the QSPI operation with the exception of NEWQP (bits [3:0]) in SPCR2. Rewriting the same value to these bits causes the RAM queue pointer to restart execution at the designated location.

If control bits are to be changed, the CPU should halt the QSPI first. With the exception of SPCR2, writing a different value into a control register while the QSPI is enabled may disrupt operation. SPCR2 is buffered, preventing any disruption of the current serial transfer. After completion of the current serial transfer, the new SPCR2 values become effective.

#### 4.3.1 QSPI Control Register 0 (SPCR0)

SPCR0 contains parameters for configuring the QSPI before it is enabled. Although the CPU can read and write this register, the QSM has read-only access.

**SPCR0** — QSPI Control Register 0

#### \$YFFC18

|        |      |    |    |    |    |      |      |      |   |   |   |   | - |   |   |

|--------|------|----|----|----|----|------|------|------|---|---|---|---|---|---|---|

| 15     | 14   | 13 | 12 | 11 | 10 | 9    | 8    | 7    | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| MSTR   | WOMQ |    | Bľ | TS |    | CPOL | CPHA | SPBR |   |   |   |   |   |   |   |

| RESET: |      |    |    |    |    |      |      |      |   |   |   |   |   |   |   |

| 0      | 0    | 0  | 0  | 0  | 0  | 0    | 1    | 0    | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

MSTR — Master/Slave Mode Select

1 = QSPI is system master and can initiate transmission to external SPI devices.

0 = QSPI is a slave device, and only responds to externally generated serial transfers.

MSTR configures the QSPI for either master or slave mode operation. This bit is cleared on reset and may only be written by the CPU, not the QSM.

WOMQ — Wired-OR Mode for QSPI Pins

- 1 = All QSPI port pins designated as output by DDRQS function as open drain outputs and can be wire-ORed to other external lines.

- 0 = Output pins have normal outputs instead of open-drain outputs.

WOMQ allows the QSPI pins to be wire-ORed, regardless of whether they are used as general-purpose outputs or as QSPI outputs. WOMQ affects the QSPI pins whether the QSPI is enabled or disabled. This bit does not affect the SCI submodule transmit (TXD) pin, which has its own WOMS bit in an SCI control register.

#### BITS — Bits Per Transfer

In master mode, BITS determines the number of data bits transferred for each serial transfer in the queue that has the command control bit (BITSE of the QSPI RAM) equal to one. If BITSE equals zero for a command, 8 bits are transferred for that command regardless of the value in BITS. Data transfers from 8 to 16 bits are supported. Illegal (reserved) values all default to 8 bits. BITSE is not used in slave mode. All transfers are of the length specified by BITS. **Table 4-2** shows the number of bits per transfer.

| Bits [13:10] | Bits per Transfer |

|--------------|-------------------|

| 0000         | 16                |

| 0001         | Reserved          |

| 0010         | Reserved          |

| 0011         | Reserved          |

| 0100         | Reserved          |

| 0101         | Reserved          |

| 0110         | Reserved          |

| 0111         | Reserved          |

| 1000         | 8                 |

| 1001         | 9                 |

| 1010         | 10                |

| 1011         | 11                |

| 1100         | 12                |

| 1101         | 13                |

| 1110         | 14                |

| 1111         | 15                |

#### Table 4-2 Bits per Transfer if Command Control Bit BITSE = 1

#### CPOL — Clock Polarity

- 1 = The inactive state value of SCK is high.

- 0 = The inactive state value of SCK is low.

CPOL is used to determine the inactive state value of the serial clock (SCK). CPOL is used in conjunction with CPHA to produce the desired clock-data relationship between master and slave device(s). QSPI clock/data timing relationships are specified in individual microcontroller user's manuals.

#### CPHA — Clock Phase

- 1 = Data is changed on the leading edge of SCK and captured on the following edge of SCK.

- 0 = Data is captured on the leading edge of SCK and changed on the following edge of SCK.

CPHA determines which edge of SCK causes data to change and which edge of SCK causes data to be captured. CPHA is used in conjunction with CPOL to produce the desired clock-data relationship between master and slave device(s). Note that CPHA is set at reset.

#### SPBR — Serial Clock Baud Rate

The QSPI internally generates the baud rate for SCK, the frequency of which is programmable by the user. The clock signal is derived from the MCU system clock using a modulus counter. At reset, BAUD is initialized to a 2.1-MHz SCK frequency (16.78-MHz system clock).

The user programs a baud rate for SCK by writing a baud value from 2 to 255. The following equation determines the SCK baud rate:

SCK Baud Rate = System Clock/

$$(2 * SPBR)$$

(4-1)

or

SPBR = System Clock/(2 \* SCK Baud Rate Desired) (4-2)

where SPBR equals 2, 3, 4,..., 255.

Programming SPBR with the values zero or one disables the QSPI baud rate generator. SCK is disabled and assumes its inactive state value. No serial transfers occur. SPBR has 254 active values. **Table 4-3** lists several possible baud values and the corresponding SCK frequency based on a 16.78-MHz system clock.

#### Table 4-3 Examples of SCK Frequencies

| System Clock<br>Frequency | Required<br>Division Ratio | Value of<br>SPBR | Actual<br>SCK Frequency |

|---------------------------|----------------------------|------------------|-------------------------|

| 16.78 MHz                 | 4                          | 2                | 4.19 MHz                |

|                           | 8                          | 4                | 2.10 MHz                |

|                           | 16                         | 8                | 1.05 MHz                |

|                           | 34                         | 17               | 493 kHz                 |

|                           | 168                        | 84               | 100 kHz                 |

|                           | 510                        | 255              | 33 kHz                  |

#### 4.3.2 QSPI Control Register 1 (SPCR1)

SPCR1 contains parameters for configuring the QSPI before it is enabled. Although the CPU can read and write this register, the QSM has read access only, except for SPE. This bit is automatically cleared by the QSPI after completing all serial transfers or when a mode fault occurs.

| Ş | SPCR1—QSPI Control Register 1 \$YFFC1 |       |    |    |    |    |   |   |   |     |   |   |   |   |   | C1A |  |

|---|---------------------------------------|-------|----|----|----|----|---|---|---|-----|---|---|---|---|---|-----|--|

|   | 15                                    | 14    | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6   | 5 | 4 | 3 | 2 | 1 | 0   |  |

| Γ | SPE                                   | DSCKL |    |    |    |    |   |   |   | DTL |   |   |   |   |   |     |  |

|   | RESET:                                |       |    |    |    |    |   |   |   |     |   |   |   |   |   |     |  |

|   | 0                                     | 0     | 0  | 0  | 0  | 1  | 0 | 0 | 0 | 0   | 0 | 0 | 0 | 1 | 0 | 0   |  |

#### SPE — QSPI Enable

- 1 = The QSPI is enabled and the pins allocated by QSM register PQSPAR are controlled by the QSPI.

- 0 = The QSPI is disabled, and the seven QSPI pins can be used as general-purpose I/O pins, regardless of the values in PQSPAR.

This bit enables or disables the QSPI submodule. Setting SPE causes the QSPI to begin operation. If the QSPI is a master, setting SPE causes the QSPI to begin initiating serial transfers. If the QSPI is a slave, the QSPI begins monitoring the PCS0/SS pin to respond to the external initiation of a serial transfer.

When the QSPI is disabled, the CPU may use the QSPI RAM. When the QSPI is enabled, both the QSPI and the CPU have access to the QSPI RAM. The CPU has both read and write access capability to all 80 bytes of the QSPI RAM. The QSPI can read only the transmit data segment and the command control segment, and can write only the receive data segment of the QSPI RAM.

The QSPI turns itself off automatically when it is finished by clearing SPE. An error condition called mode fault (MODF) also clears SPE. This error occurs when PCS0/ $\overline{SS}$  is configured for input, the QSPI is a system master (MSTR = 1), and PCS0/ $\overline{SS}$  is driven low externally.

To stop the QSPI, assert the HALT bit in SPCR3, then wait until the HALTA bit in SPSR is set. SPE may then be safely cleared to zero, providing an orderly method of quickly shutting down the QSPI after the current serial transfer is completed. The CPU can immediately disable the QSPI by just clearing SPE; however, loss of data from a current serial transfer may result and confuse an external SPI device.

DSCKL — Delay before SCK

This bit determines the length of time the QSPI delays from peripheral chip-select (PCS) valid to SCK transition for serial transfers in which the command control bit, DSCK of the QSPI RAM, equals one. PCS may be any of the four peripheral chip-select pins. The following equation determines the actual delay before SCK:

PCS to SCK Delay = [DSCKL/System Clock Frequency] (4-3)

where DSCKL equals {1,2,3,... 127}.

#### NOTE